《魔物娘的相伴日常》作為一部以人與魔物娘共處為主題的奇幻喜劇動(dòng)畫(huà),其人物設(shè)計(jì)確實(shí)引發(fā)了觀眾的廣泛討論。一方面,制作方試圖通過(guò)夸張化、萌系化的手法呈現(xiàn)各種魔物娘角色;另一方面,這種設(shè)計(jì)風(fēng)格也帶來(lái)了不少爭(zhēng)議和不適感。

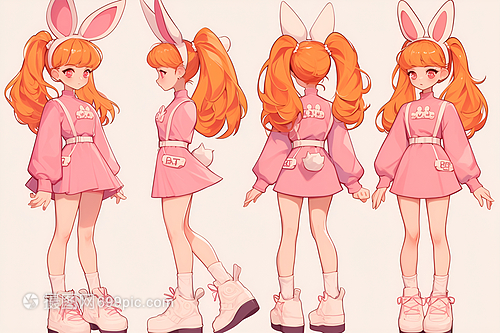

從視覺(jué)表現(xiàn)來(lái)看,動(dòng)畫(huà)采用了典型的日式萌系畫(huà)風(fēng),但在魔物娘的設(shè)計(jì)上刻意強(qiáng)化了非人特征。比如拉米婭族的米亞保留了完整的蛇身,哈比族的帕皮則擁有完整的鳥(niǎo)類(lèi)翅膀和爪子。這種設(shè)計(jì)雖然忠實(shí)于原作設(shè)定,但在動(dòng)畫(huà)動(dòng)起來(lái)時(shí),某些場(chǎng)景確實(shí)會(huì)讓人產(chǎn)生生理上的不適感。特別是在日常互動(dòng)場(chǎng)景中,人類(lèi)與魔物娘的身體差異被放大,有時(shí)會(huì)造成視覺(jué)上的不協(xié)調(diào)。

人物造型的色彩運(yùn)用也值得商榷。制作方使用了高飽和度的配色方案,本意可能是為了突出奇幻氛圍,但過(guò)多鮮艷色彩的堆砌反而讓畫(huà)面顯得雜亂。特別是在多位魔物娘同框的場(chǎng)景中,各種亮色相互沖突,缺乏視覺(jué)重點(diǎn),容易造成審美疲勞。

動(dòng)作設(shè)計(jì)方面,制作組試圖通過(guò)夸張的肢體語(yǔ)言和表情來(lái)制造喜劇效果,但這種做法有時(shí)顯得過(guò)于刻意。魔物娘們的動(dòng)作常常突破常規(guī)范疇,雖然符合非人設(shè)定的邏輯,但過(guò)度夸張的表現(xiàn)方式反而削弱了角色的真實(shí)感,讓觀眾難以產(chǎn)生共鳴。

值得注意的是,這種設(shè)計(jì)困境其實(shí)反映了跨界題材創(chuàng)作的普遍難題。如何在保持奇幻設(shè)定的同時(shí)不讓觀眾產(chǎn)生排斥感,如何在萌系畫(huà)風(fēng)與非人特征之間找到平衡,都是制作組需要面對(duì)的挑戰(zhàn)。《魔物娘的相伴日常》的人物設(shè)計(jì)或許未能完美解決這些問(wèn)題,但其探索本身也為我們思考動(dòng)畫(huà)人物設(shè)計(jì)提供了有價(jià)值的案例。